Allegro PCB进阶设计第一期:规则驱动设计

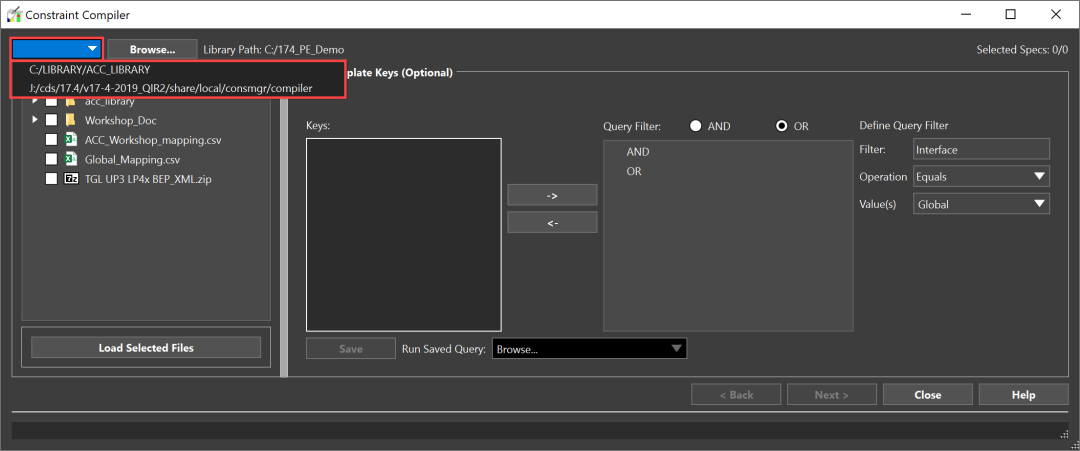

Q 间距规则中的Through via和BB via(Buried/Blind Via)有什么区别? 答:Through via指通孔,贯穿整个PCB; BB via(Buried/Blind Via)是盲/埋孔:盲孔是从表层贯穿到PCB的一个内层;埋孔是从一个内层到另一个内层。 两者最大的区别是“盲/埋孔”表层看不到孔。 Q 如何设置检查盲/埋孔焊盘(或孔)相交规则? 答:同名网络规则和DFM规则都可以约束盲/埋孔的设计—— BB via(Buried/Blind Via)to Micro Via。 Q 如何设置等长信号组间之间的长度控制?比如USB有三个差分对,差分组内要求20,组间要求100。 答:差分组内长度常用差分线的Tolerance来控制,组间要求用绝对长度约束或者相对长度约束都可以设置。用绝对长度时,控制最大最小值;用相对长度时选择其中一组作为target,其他组跟target在100mil内等长。 Q csv文件的模板如何提取? 答:csv文件提取路径如下: \share\pcb\examples\acc\Starter_Template Q Allegro Constraint Compiler是否有推荐的规则模板? 答:请到如下路径查找: install_directory>\share\pcb\examples\acc\Starter_Template Q 孔距离板边距离设置如何约束? 答:用Manufacturing下面的DFF规则中Outline to这一类规则可以约束。 Q 设计规则器里设置之前必须设置好DC、器件的属性吗? 答:DC Net影响的时直流电压,如果要进行的设计涉及这个值,就需要设定。器件属性源于封装库,如果封装设计时是正确的,就可以不改动。 Q Allegro Constraint Compiler 现在只支持物理间距与电气规则,未来会支持DFM吗? 答:感谢反馈,我们会综合考虑客户反馈和产品开发项目的安排。新的功能和计划请以官网、以及我们后续即将发布的新版本信息为准。 Q 为何在设置Net Class之后还要设置一个net group? 答:Net Class是把信号进行了分类;Net Group可把需要进行长度匹配的对象设定为一个匹配组。 Q 差分线中的Min Line Space是指什么?Min Line Space和Neck Gap一般设置为相同数值,有不同数值的情况吗? 答:Min Line Space是最小线间距。Min Line Space和Neck Gap有设置为不同数值的情况。依据设计的实际需求来定。 Q 什么是基于区域的DFA规则? 答:PCB的不同区域可以设定不同的DFA规则。 Q 高速信号的特征阻抗是否可以设置?是否与材料有关系? 答:特征阻抗规则是可以设定的,在Constraint Manager的电气规则下设定。特征阻抗跟材料有关系。 Q 如何建立 Allegro Constraint Compiler 的csv数据库? 答:这要看设计的实际需求。比如把自己的常用接口规则累积起来,形成自己特有的规则库,需要用的时候可直接调用。 Q Route Keep in 能否按照层设置?这样采用正片设计,电源层可以内缩。 答:Route Keep in是添加到all的。 Q 多个DDR的地址时钟线如何设置对内等长? 答:把需要设置对内等长的信号设定为一个Group。 Q Allegro Constraint Compiler 中如何导出? 答:当前Allegro® PCB Designer SPB17.4 版本可以导入规则,暂不支持导出基于模板的规则。 Q Allegro Constraint Compiler 规则可以把待加载文件放到服务器上吗? 答:通过设定accpath可以实现规则加载。设定路径后即可在导入界面找到该路径,如下图所示。