如何使用Allegro直接添加相对传输延迟的等长规

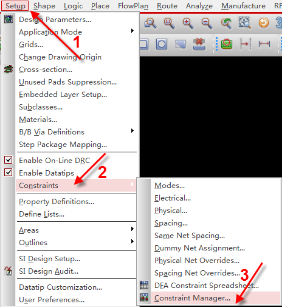

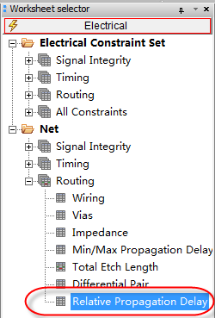

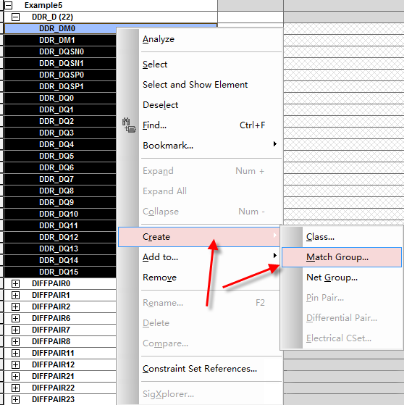

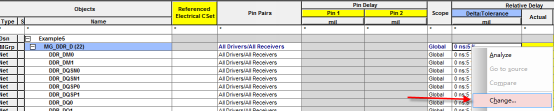

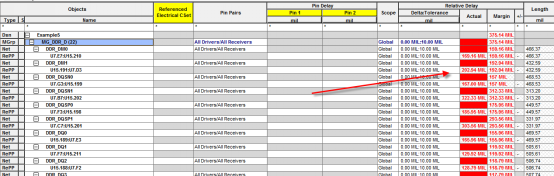

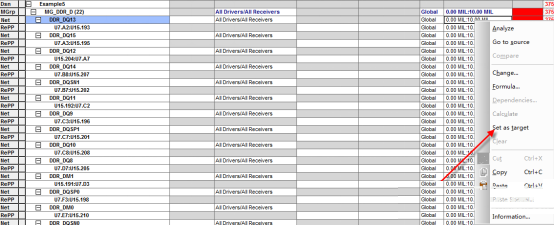

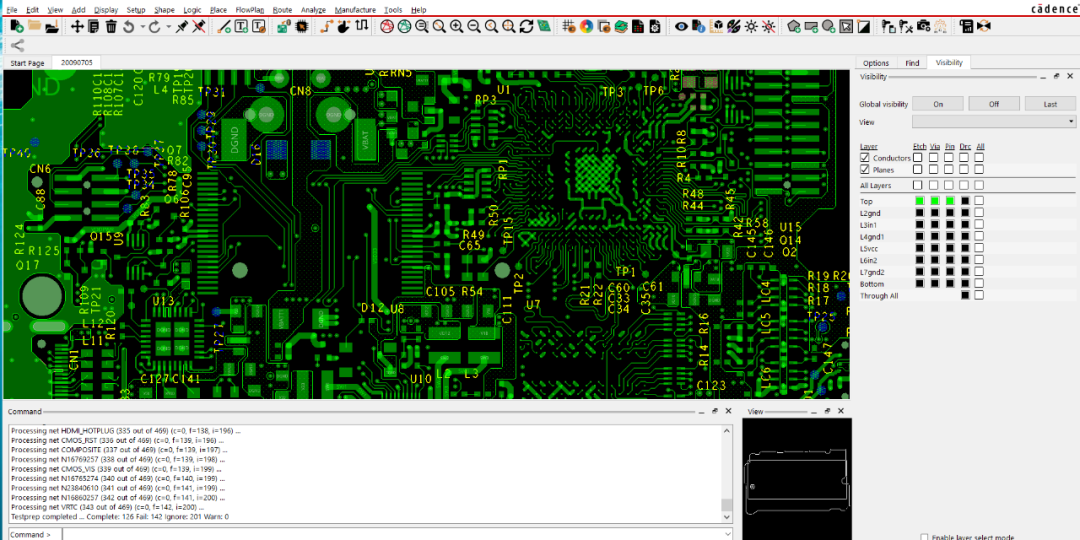

打开规则管理器,执行菜单命令Setup-Constraints,在下拉菜单中选择Constraint Manager,如图1所示,进入到规则管理器中; 图1 规则管理器示意图 进入到规则管理器之后,在CM左侧的目标栏中选择Net,在Net中选择相对传输延迟选项Relative Propagation Delay,如图2所示; 图2 相对传输延迟设置示意图 选择需要创建等长的信号线,或者是事先将需要创建等长的信号线加好Bus,直接全部选中,点击鼠标右键,执行菜单命令Create-Match Group,创建等长集合,如图3所示; 图3 创建等长集合示意图 在弹出的界面中,输入需要创建的等长集合的名称,见名知意,如:“MG_DDR_D”,取好名称之后,点击按钮,则等长的集合就创建完毕了,创建好之后,在误差那一栏,选中最上面的根目录,点击鼠标右键,点击Change命令,对所设置的等长集合的误差进行修改即可,如图4所示; 图4 误差设置示意图 设置好误差之后,比如±10mil,点击OK按钮,则这一组需要做等长的信号线的规则就添加好了,如图5所示; 图5 等长列表示意图 等长添加好以后,选择一根合适的信号线,点击右键,设置为目标线,则所有的信号线就按照这个线为基准,在误差范围进行等长即可,如图6所示; 图6 设置目标线意图 通过上面的学习让我们看到了如何使用Allegro直接添加相对传输延迟的等长规则。阅读完这篇文章的小伙伴可以自己去试一试这个功能。下期给大家分享如何使用Allegro精准定位删除Out of data shape铜皮框。