SiP Layout

产品介绍

概述

高性能消费类电子产品制造商正转向到SIP设计,因为它提供了一些显若优势,如增加功能密度,整合不同的芯片技术,低功耗,改善信号质量/完整性,并且易于集成到PCB系统中。然而,SIP设计还需要广泛的各种领域的专家设计人才,通过互连驱动的方法,将多个高引脚数的芯片与一个单一基板的集成简化。Cadences净协同设计技术允许企业采用专业的SIP工程设计能力为主流产品进行开发。

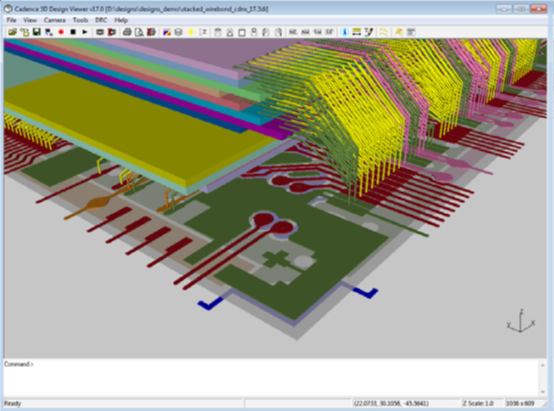

SIP layout为封装基板设计工具,可以完成从简单到复杂不同层次的基板设计,能完成多IO管脚、高密度、多芯片堆叠、三维封装等复杂的封装设计,提供多重腔体、复杂形状封装形式的支持。支持所有的封装类型,包括QFP、PGA、BGA、CSP等封装类型。提供约束和规则驱动的版图设计环境。它包括布线、Wire Bonding、系统级设计优化、制造准备、整体设计验证。该环境集成了IC/封装/I/O布局性能、三维裸片堆叠结构生成与编辑性能。另外,完善的设计规则检查(DRC)可支持层压、陶瓷、及镀膜技术复杂和独特的要求。

功能特征

支持表格化的裸芯片DIE Pad信息导入接口

裸片堆叠创建/编辑,以进行快速堆叠装配与优化

IC、基板、系统级封装的I/O填补环/阵列协同设计与连接优化

允许IC和基板的互连分配和优化

在Flip Chip的设计中,支持自动扇出和布线,减少冗长乏味的、耗时的人工设计工作

使用有IP保护的DIE Abstract在芯片、基板及系统间进行IC bump精细化设计

允许芯片与基板间的IO分配和优化

通过倒装芯片的自动布线扇出方法,可以减少繁琐好使的手动扇出编辑工作

以规则驱动HDI设计,消除潜在的设计隐患

灵活便捷的Wire Bonding编辑器

自动键合环对称与非对称编辑能力

独特的金手指编辑与推挤功能

支持真实的线的弧形驱动Wire Bonding编辑,更真实的接近生产DFM要求

Wire Bonding弧形线键合线创建及弧形线外形库

支持全面的Wire Bond规则检查,消除潜在的装配隐患,并可导出Wire bond的描述文件

提供三维设计查看器,以获得精确的三维视图验证、设计复审纠错。

3D design viewer and 3D DRC

SiP Digital Architect

SiP Digital Architect为早期互连及约束创建提供了一个设计环境,驱动die abstract,芯片堆叠,转接板与封装基板的协同设计,他管理编辑互联中的任何变化或pin/焊球信号分配并为LVS提供主要的逻辑定义,它能够快速定义SIP系统连接关系,同时管理不同来源的信号名的映射关系。

快速定义SIP系统连接关系,同时管理不同来源的信号名的映射关系

Virtuoso SIP Architect

为射频IC、SIP基板、嵌入的射频无源元件等组件提供一个单一的、顶层的Virtuoso原理图与仿真环境

支持RF/Digital/Analog IC设计团队与SIP基板设计团队之间的双向ECO和LVS流程

支持在Virtuoso原理图中创建板级射频无源参数化单元(P-cell)

从Virtuoso Layout Editor直接导出DIE封装,可以加快设计

自动从Cadence SiP Layout 中将寄生参数反标回测试平台

Virtuoso SiP Architect 提供了一个全功能的混合信号设计流程

XtractIM

Cadence Allegro Sigrity Package Assessment and Extraction的封装分析与建模解决方案可以进行早期的性能评估,直流与交流电源网络分析,使用混合求解器或三维全波求解器可提取封装上全部或部分信号的等效电路模型,从而获得整个封装的模型。封装评估工具可以快速检测封装设计中的以下问题:检测电感过大的封装引脚,阻抗超标及过耦合等。电源感知混合求解器模型企图引擎,可以提取完整的耦合信号与电源网络RLGC与S参数模型。全波求解器可以对IC封装内的详细的高频互联结构进行模型提取。

支持Flip Chip、Wirebond,及混合设计方式同时支持。

支持仿真各种类型的封装,如Single-Die、Stacked-Die、Package-on-Package、Multiple side-by-side Die 、Leadframe类型的封装

支持将On-Chip 的IC 级模型以及In-Package 的去耦电容与物理的封装模型一起进行综合模型提取

支持生成标准的IBIS 模型

支持生成单级、多级宽带RLC 模型

支持产生具有信号间,以及信号与电源/地之间的电磁耦合效应的IBIS RLC 矩阵模型

支持产生具有电磁耦合效应的等效SPICE RLGC T 或Pi 电路模型

支持显示封装的RLC 分布

压降分析可考虑元件本身与焦耳热的联合系统电热分析,空间依赖性温度分布,及平面过孔和互连线的电流密度分析。

更多信息详见Cadence Sigrity XtractIM、PowerDC、PowerSI等产品介绍。