第9周:最坏情况分析

最坏情况分析是用于确定电路性能影响最关键的元件,估算出电路性能相对标称值时的最大偏差。最坏情况分析过程:

进行标称值的电路仿真。

计算灵敏度,将各个元器件逐个变化进行电路仿真,如果有n个元器件参数需要变化,则需要进行n次分析。

得到灵敏度后,再做一次最坏情况分析,各元件选择各器件取最大容差值进行计算,得到结果。

所以如果电路中有n个变量的话,最坏情况分析其实是进行了n+2次的电路性能分析。本期模拟电路分析延用上一期窄带通滤波器的实例,利用最坏情况分析确定哪些元件对电路性能影响最大,以及输出电压的最大和最小值。

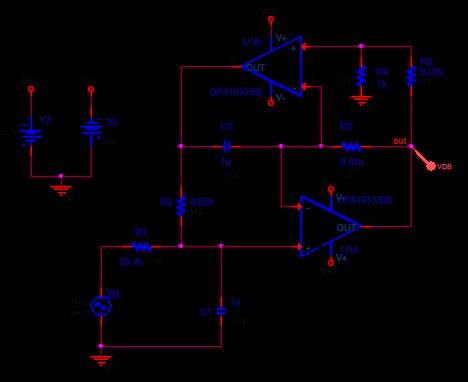

图9.1 本期实例电路

1

模拟电路的最坏情况分析

最坏情况分析与蒙特卡洛分析一样,它与交流分析、直流分析或者瞬态分析同时进行,在绘制原理图时也需要通过元器件属性编辑器对各元器件的容差进行设置,方法跟上一期一致。

01

仿真参数设置

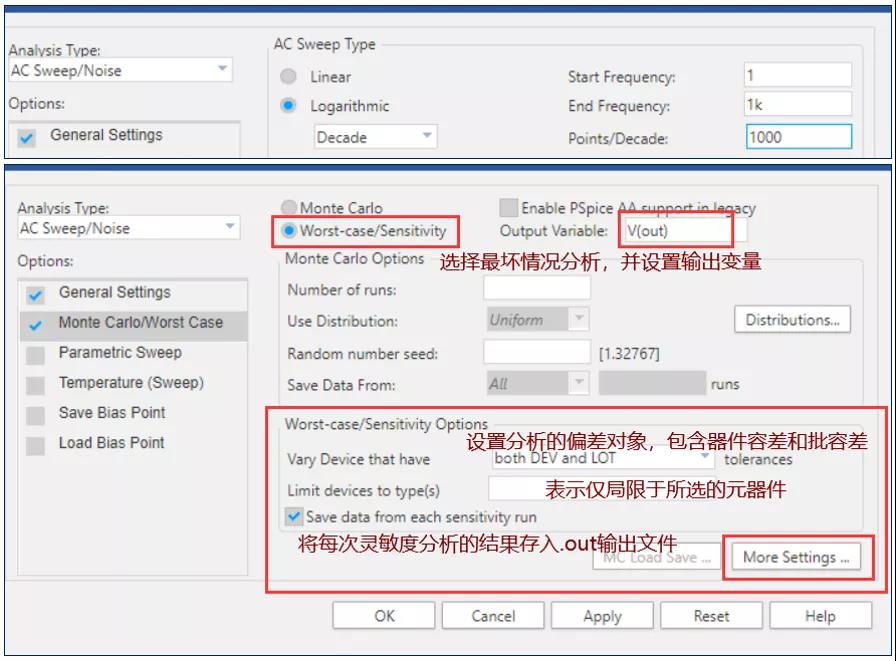

首先仍然是新建仿真文件,然后点选菜单PSpice/Edit Simulation Profile,或者点击相应菜单图标,出现设置参数的界面,选择AC Analysis,设置频率参数,频率范围1Hz到1kHz,点频1000。并同时勾选上Monte Carlo/Worst Case,具体设置如图9.2所示:

图9.2最坏情况分析设置对话框

02

输出结果的设置

图9.2中点击More Setting出现图9.3所示的对话框:

图9.3 最坏情况分析的更多选择

图9.3中的下拉菜单,表示分析时选择输出内容。各选项意义:

选择最后两项时,还需要在Threshold Value后面的编辑框中设置域值。本例选择Max,在输出文件中能看到每个波形的最大值,结果在下文图9.9中体现。

在Worst-Case direction中设定最坏情况分析的朝向,Hi 表示分析的输出结果朝高于标称结果偏移,Low 表示分析的输出结果朝低于标称结果偏移。下文图9.5和图9.7分别呈现这两种结果,大家应该就能明白具体含义了。

2

分析最坏情况结果

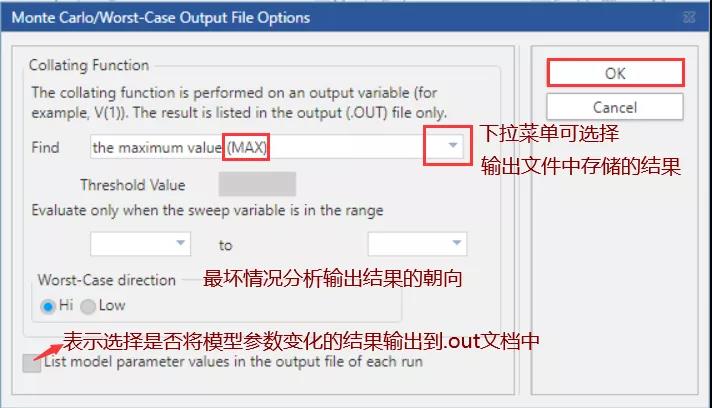

图9.2点击确定后,运行仿真。屏幕会出现图9.4的画面,此对话框告知模拟结果的波形资料,因为在图9.2中,我们将“Save data from each sensitivity run”前的复选框勾选上,于是出现每个变量变化的输出波形,以及第一次标称值下和最坏情况下的结果,实例电路中设置了七个带容差的器件,因此得到7+2个结果。

图9.4 模拟结果的波形资料

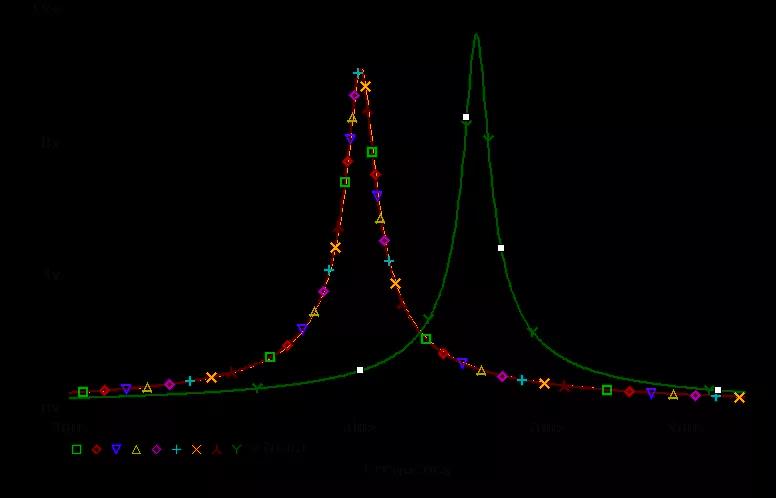

按“OK”后得到输出波形,为了观察清楚,图9.5的横坐标经过了调整。

图9.5 输出结果朝向选择HI的仿真分析结果

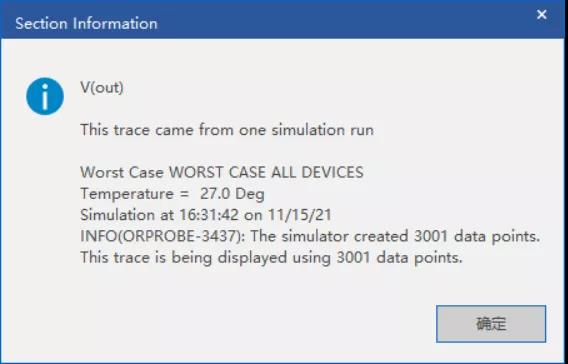

点击最高的那条幅频特性曲线,右键选择“Trace information”,打开该曲线的属性,可以看出这是最后一次最坏情况分析的结果,说明这是趋势高于正常曲线的最坏情况。

图9.6 最坏情况曲线信息

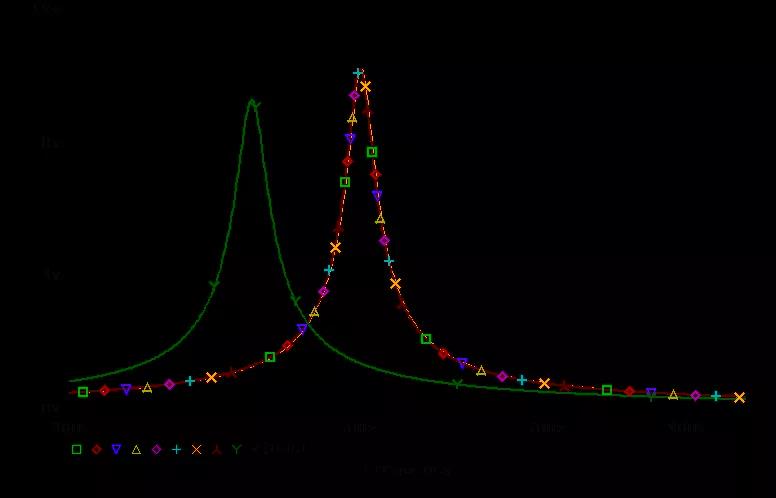

如果在图9.3对话框中Worst-Case direction选择Low,得到的是图9.6的曲线,可以看出最坏情况的结果的趋势是低于正常曲线的。

图9.7 输出结果朝向选择Low的仿真分析结果

01

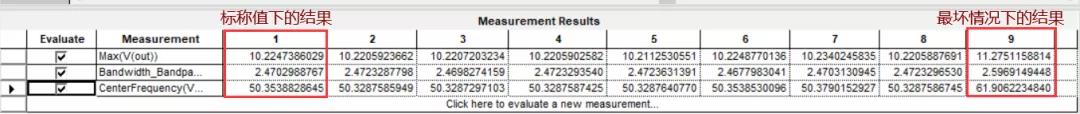

电路特性函数的数值

若想得到电路特性函数的数值可以选择Trace → Evaluate Measurement,设置相应的测量函数,就可以在波形显示窗口下显示每一条波形的数值。图9.8是在图9.5状态下的输出结果,可以看到最后一列的数值是高于第一列标称值下的数值。

图9.8 特性函数的数值

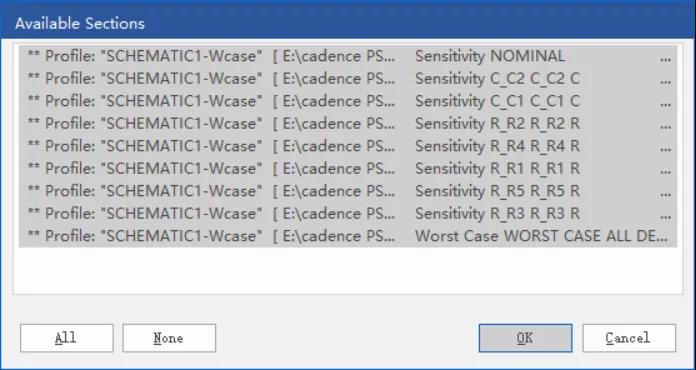

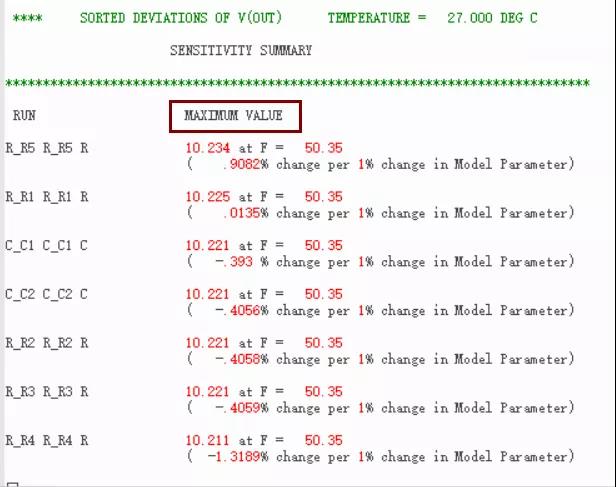

02 灵敏度分析结果 选择打开输出文档,点击 View → Output File,通过向下拖动文档内容,可以看到图9.9所示的灵敏度分析结果。

图9.9 灵敏度分析结果

仿真列出电路中七个元件根据容差变化时,V(out)的输出结果的最大值,从图9.9中可以R5和R1变化时输出电压比标称值时大,而C1、C2、R2、R3和R4变化时输出电压均比标称值小。

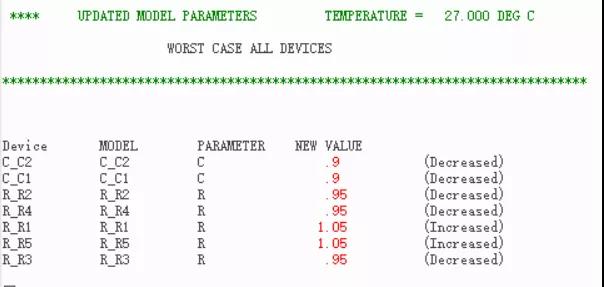

03 最坏情况的文字结果 输出文件继续向下拖动,还能看到最坏情况分析中各元器件容差极限取值。如图9.10所示,可以看出引起输出增大的器件取容差正的最大值,引起输出减小的取容差负的最大值。

图9.10 最坏情况分析时元器件容差极限值列表

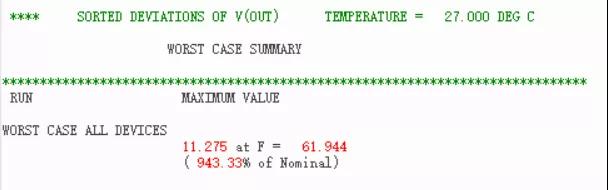

在图9.10所示的容差极限取值下,得到输出电压的最坏情况。结果在输出文件的底部,我们能看到最坏情况仿真分析概要,如图9.11所示,从图中可以看出最坏情况时中心频率为61.944Hz,偏离标称值约943.33%。

图9.11 最坏情况仿真分析概要

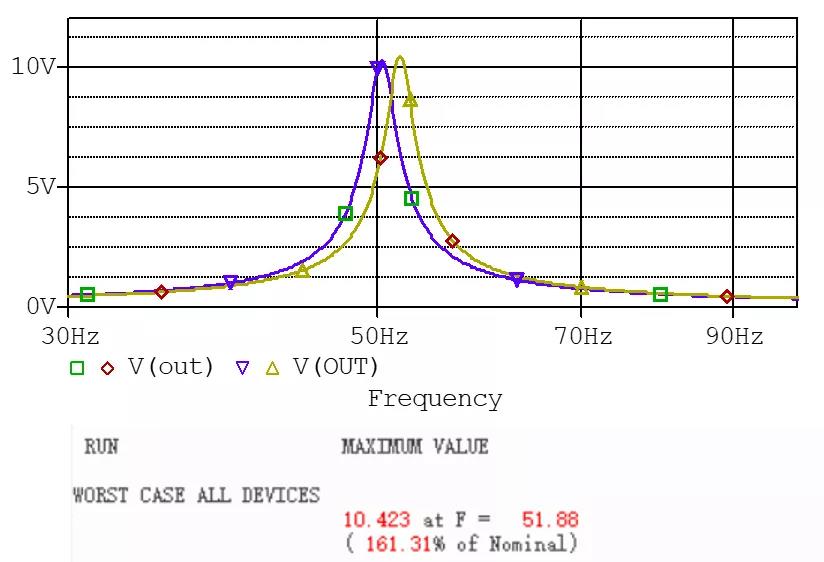

若将电路中电阻和电容的容差均修改为1%,重新运行,可以看到最坏情况和标称状态的偏差缩小。

图9.12 减小容差后的仿真结果

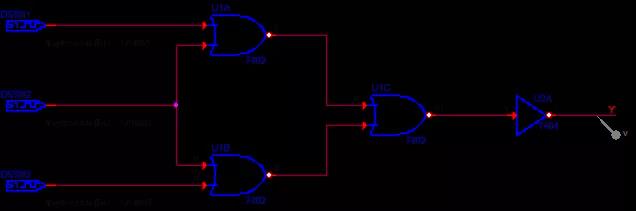

3 数字电路最坏情况逻辑模拟分析 像模拟电路最坏情况一样,数字电路同样提供了最坏情况逻辑模拟分析,只不过此时考虑的不再像模拟电路那样着重其输出值的偏移量,而将重点放在时序问题上。 数字逻辑器件的标准参数值称为标称值,而实际的器件参数值总存在一个误差范围,同种器件的误差又各有不同,因此不能保证按同一电路设计组装起来的各电路性能相同。逻辑器件输出端对输入端信号的反映有一个延迟时间,该时间对于同种器件不同的个体也有一个范围,这个时间范围称为模糊时间。最坏情况逻辑模拟就是考虑到这个时间,分析其对电路各电信号的影响,确定是否会引起不正常的逻辑关系。 如果最坏情况分析表明在设定的误差范围内有逻辑问题,说明电路各器件在分析时设定的误差范围内成品率低,这并不表明成品率是0。如果逻辑电路器件既通过逻辑模拟,又通过最坏情况模拟,说明电路对其内部各元器件的误差有足够宽的容限,这样设计并组装的电路成品率将很高。 在进行数字逻辑分析时,对逻辑器件的延迟时间可设定最小值、最大值或典型值。进行最坏情况分析是取其最大值和最小值之差,这便是模糊时间的范围。信号在不同的逻辑器件中传送,各器件的模糊时间将累积。 以图9.13简单的一个数字电路为例来说明如何进行最坏情况分析。

图9.13 组合逻辑电路

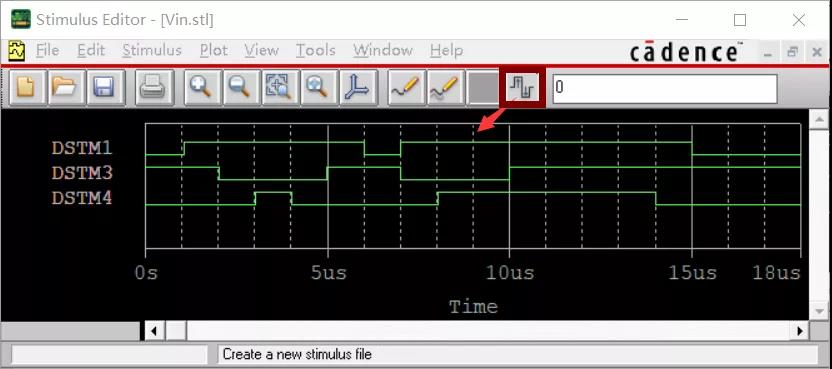

对输入的三个信号采用图形编辑器进行设置,PSpice的图形编辑器在开始菜单中找到的PSpice Stimulus Editor 17.4,选择新建一般信号源(signal),设置如图9.14所示的三个输入信号。

图9.14 输入信号的图形设置

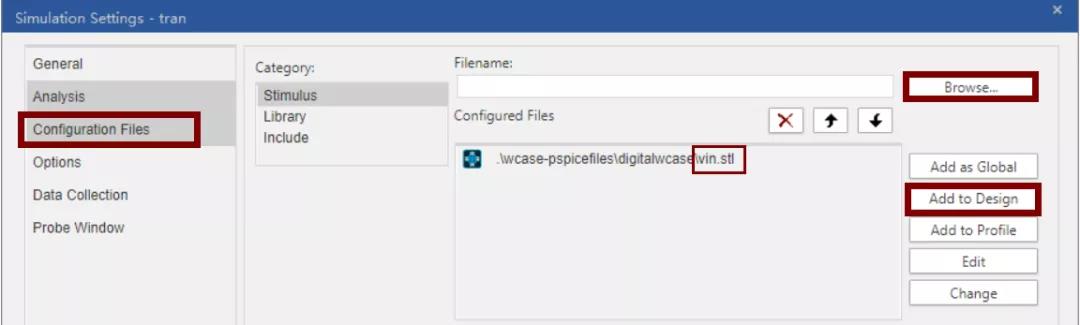

编辑好输入信号后,将波形文件存储在工程文件下,并在布局文件(Configuration File)中将波形文件添加到工程中。如图9.15所示。

图9.15 添加波形文件到设计工程中

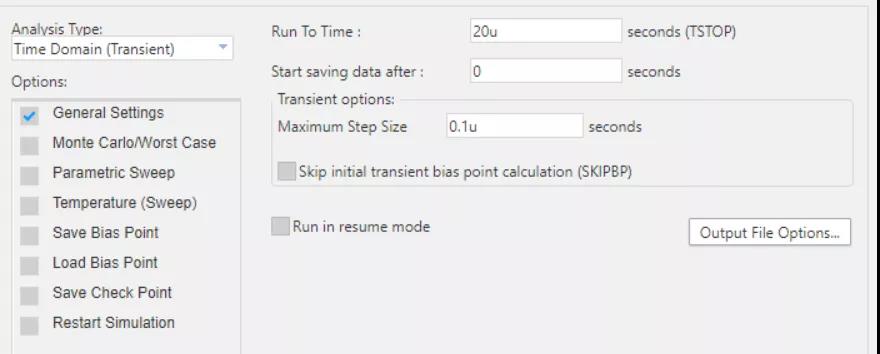

同时设置瞬态分析,如图9.16所示。

图9.16 瞬态分析设置

运行得到波形结果为图9.17。